SoC 전력 관리를 위한 PMIC 기술

보다 밀도 높은 패키징과 더 많은 연결성을 지원하는 혁신적인 기술과 애플리케이션은 기존 프로세서와 해당 전력 시스템의 성능을 더욱 끌어올려 줍니다. 이러한 프로세서는 점점 더 많은 수의 오디오, 비디오, 고화질(HD) 그래픽, 스트리밍, 게임 등 모든 것을 사용하여 컴퓨팅을 지원해야 합니다. 콘텐츠의 양과 질이 높아질수록, 보다 작은 면적에서 더 높은 성능을 제공하길 바라는 요구들 역시 높아집니다. 이처럼 사용자 중심적인 접근방식은 더 높은 통합 수준을 끊임없이 요구하기 때문에 기술 개발의 제약요인이 됩니다.

비용은 더욱 줄이면서 보다 높은 성능을 달성해야 하다 보니 엔지니어들은 시스템온칩(SoC)를 개발해야 할 수밖에 없습니다. SoC는 많은 시스템 기능을 하나의 IC에 통합함으로써 전력 소모, 비용, 노력을 줄여줄 뿐 아니라, 예컨대 비디오 및 그래픽 처리 같이 심도 있는 전문성을 요구하는 기능들을 구현하는 데 필요한 기술 지식에 대한 요구도 줄여줍니다. 여건에 맞는 비용으로 고성능을 달성하려면 제조회사는 16nm 또는 14nm 이하의 딥 서브미크론 CMOS 공정으로 SoC를 개발해야 합니다.

이러한 SoC는 고전류를 공급하기 위한 전원공급장치가 필요한데, 이는 고급 서브미크론 CMOS 공정에서 실현하기 어려운 과제일 수 있습니다. 전원공급 회로는 고전류를 처리하고 디지털 코어 전압에 비례하는 고전압을 견딜 수 있도록 대형 트랜지스터를 필요로 합니다. 이러한 속성은 디지털 회로에 사용되는 트랜지스터와 관련한 속성과는 전혀 부합하지 않습니다. 따라서 디지털 회로와 동일 다이에 전원공급장치를 구현하는 것은 기술적으로 어렵거나 불가능하며, 설령 가능하다 할지라도 비경제적일 가능성이 큽니다. IC 설계에서는 이 같은 비양립성이 늘 존재하긴 했지만, 첨단 프로세서들이 갈수록 더 낮은 CMOS 공정에서 구현되면서 이러한 현상은 더 심해지고 있습니다.

-

-

[마우저 일렉트로닉스] SoC 전력 관리를 위한 PMIC 기술 (출처: graphicINmotion/Shutterstock.com)

-

이번 포스팅에서는 NXP i.MX 8M 프로세서 제품군(미니(Mini)와 나노(Nano))과 로옴(ROHM)의 BD71847/BD71850을 가지고 SoC-PMIC(Power Management Integrated Circuit) 동시 설계 시 고려사항의 관리 및 최적화에 대해 알아보겠습니다. 예시 모델로 이 솔루션들을 선택한 이유는 이들이 제공하는 기능, 낮은 BOM(Bill of Material) 비용, 그리고 소형 풋프린트 특성 덕분에 OEM들이 스마트한 커넥티드 디바이스를 신속하게 개발 및 생산할 수 있기 때문입니다.

-

트레이드오프와 대안

SoC 상에서 시스템 레벨의 전력 통합이 늘어나면 그에 따라 다음과 같은 몇 가지 이슈들이 발생합니다:

▶ 설계 유연성 감소

▶ 최적화한 시스템 효율의 저하

▶ 개발 및 BOM 비용 상승

▶ 출시 기간 연장

이러한 트레이드오프는 첨단 프로세서와 그를 위한 전원 서브시스템을 구축하는 데 있어서 시스템 수준의 기술혁신 기회를 열어 줍니다.

-설계 유연성 향상 방법

NXP i.MX 8M/8미니/나노에는 DC/DC 컨버터나 LDO(Low-dropout Regulator)가 통합되어 있지 않습니다. 유사한 SoC들도 DC/DC 컨버터를 통합하고 있지 않지만, 많은 사람들은 외부 전원 레일을 프로세서 코어에 맞게 더 낮은 전압으로 변환하기 위해 온칩 LDO를 사용합니다. 즉, 동적 전압 및 주파수 스케일링(DVFS)을 코어에 적용하는 것이죠. DC/DC와 LDO를 칩에서 떼어 냄으로써, SoC 설계 엔지니어들은 예컨대 프로세서 코어, 캐시, 오디오/비디오 하드웨어 가속기 등 디지털 기능에 최적화된 값비싼 14nm 실리콘 면적을 완전히 활용할 수 있게 됐습니다. 온칩 전력관리 요건에 대한 제약이 없다면, (외부) 전원 아키텍처를 자유롭게 활용함으로써 프로세서 개발이 보다 용이해질 것입니다. i.MX 8M에 꽤 많은 수의 파워 레일 수가 필요하다(8개의 벅 컨버터와 7개의 LDO)는 점을 고려하면 쉽게 이해가 될 것입니다.

한편, ROHM PMIC 설계 엔지니어들은 전력관리 기능에 최적화된 ROHM의 130nm BCD(Bipolar-CMOS-DMOS) 공정으로 전원 회로를 구현했습니다. 각 팀은 해당 프로젝트에 가장 적합한 공정기술과 IP를 자유롭게 사용할 수 있었습니다.

-시스템 효율성 향상 방법

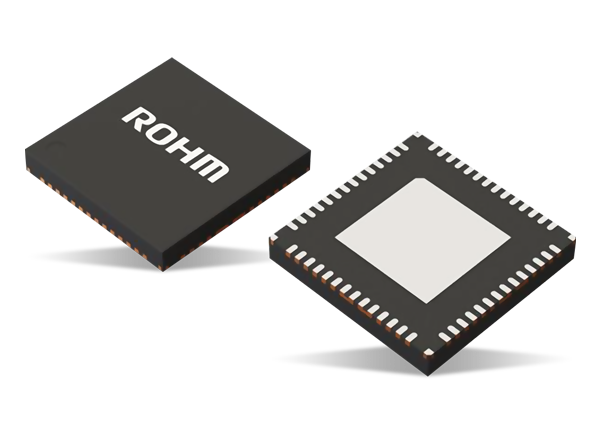

130nm BCD 공정에서 전원 회로를 구현하면 BD71847AMWV/BD71850MWV(그림 1)의 벅 컨버터가 0.7V ~ 3.3V 출력 전압에 대해 최대 95%의 효율을 달성할 수 있습니다. 시스템 레벨에서의 효율성은, DVFS를 프로세서 코어에 직접 적용하기 위해 외부 DC/DC를 사용할 때 더욱 향상됩니다. 결국 DVFS용 온칩 LDO가 있는 외부 DC/DC를 사용하는 것은 2단계 변환에 해당하므로, 2단계에서는 추가 손실이 발생합니다.

흔히 간과되는 특징은 출력 전압의 정확도(±1.5%)입니다. 출력 전압 조정 단계(10mV 간격)에서 더 높은 분해능과 함께, 전력 관리자 소프트웨어는 전력 소비를 최소화하도록 전력 레일의 출력 전압을 최저 수준으로 정밀하게 설정할 수 있으며, 그래도 여전히 해당 전력 레일에서 구동되는 서브시스템이 적절한 주파수에서 작동하도록 할 수 있습니다.

-

[그림 1] ROHM 세미컨덕터의 BD71850MWV PMIC는 i.MX 8M 나노 프로세서가 지원하는 전원 모드들과 호환되는 시퀀서는 물론, i.MX 8M 나노 프로세서 및 시스템 주변기기들이 요구하는 모든 전력 레일을 통합하고 있어, 개발 시간을 대폭 단축하고 크기를 줄이며 애플리케이션 설계를 간소화할 수 있습니다(출처: 마우저 일렉트로닉스).

-개발 및 BOM 비용 절감 방법

기능 추가, 또는 제품의 크기와 무게 축소에 대한 시장의 지속적인 압박 때문에, 엔지니어들은 IC에 더 많은 기능을 통합하고 신뢰성을 높이기 위한 방법을 끊임없이 찾고 있습니다. 그러나, 통합 수준을 높일수록 개발 비용과 다이 비용도 늘어날 수 있습니다. SoC 개발과 전력관리 기능 개발을 분리하면 각각의 작업을 최적의 속도로 진행할 수 있습니다. 설계, 검증, IC 배치에서부터 IC 제조에 이르기까지 프로세스의 모든 단계는 보다 간단하고 빨라지며, 처음에 양품 반도체를 확보할 수 있는 기회도 향상될 것입니다. 또한 보다 저렴한 (BCD)공정에서 전원 기능을 구현할수록 (총)다이 비용도 더욱 낮출 수 있습니다.

-출시 기간 단축 방법

다른 많은 하이테크 사업들과 마찬가지로, 출시 기간은 매우 중요합니다. 애플리케이션 프로세서와 같은 고도로 복잡한 소자의 경우, 디지털 프로세싱 요소(CPU, 하드웨어 가속기)와 전력관리처럼 근본적으로 양립할 수 없는 기술들의 개발을 분리하여 개발 노력과 위험 부담을 줄임으로써 출시 기간을 단축할 수 있습니다.

SoC용 프로그래머블 PMIC 설계 시 고려사항은 사용자 경험과 제품 개발에서 트레이드오프를 제공합니다. NXP의 8M/8MM/나노와 ROHM의 847/850은 제품 수명주기의 처음부터 끝까지 성공적인 동작을 가능하게 하는 솔루션을 제공합니다. 이들 제품은 스트리밍 미디어 박스와 동글에서부터 AV 수신기와 무선 사운드바, 산업용 HMI, SBC, IPC, 그리고 패널 PC에 이르는 다양한 애플리케이션에서 강력한 경쟁력을 구현할 수 있게 합니다. 이 반도체 제품들은 설계 유연성과 출시 기간 등 제조사 친화적인 자산을 통해 성능이나 가격 같은 사용자 입장에서 매우 결정적인 특성들을 최적화합니다. 이들 제품은 통합되지 않은 소자들의 유연성과 고도로 통합된 PMIC-SoC의 사용 편의성 사이의 결정적인 균형을 보여주는 제품들입니다.