마이크로컨트롤러 성능을 향상시키는 구성가능 로직(CLB)

오늘날의 전자 시스템 설계는 그 어느 때보다도 더 높은 성능, 추가 기능, 더 작은 폼팩터, 더 낮은 전력 소모, 더 낮은 비용, 혹은 이 모든 것들의 조합을 요구합니다. 이러한 과제를 해결할 수 있는 방법 가운데 하나는 구성 가능한 로직(configurable logic)을 활용하는 것입니다. 구성 가능한 로직은 마이크로컨트롤러(MCU) 안에 작은 FPGA(field programmable gate array)가 들어 있는 것과 비슷합니다. 논리 기능을 처리하기 위해 소프트웨어나 외부 하드웨어에만 의존하는 대신, 설계 엔지니어는 MCU 내부에 맞춤형 하드웨어 기반 기능을 직접 포함할 수 있습니다. 이렇게 하면 외부 부품에 대한 의존도를 줄일 수 있을 뿐 아니라 처리 속도를 높이고 전력 효율을 최적화할 수 있습니다.

이 글에서는 MCU에서 구성 가능한 로직이 제공하는 장점과 마이크로칩 테크놀로지(Microchip Technology)의 방대한 솔루션을 살펴보겠습니다.

마이크로컨트롤러 성능을 향상시키는 구성가능 로직(CLB) (출처: Archara / stock.adobe.com; AI로 생성)

성능 향상

MCU 전력 소모를 최소화하는 것은 시스템의 전체 전력 소모에 큰 영향을 미치기 때문에 매우 중요합니다. MCU는 시스템의 두뇌 역할을 하므로, 올바른 MCU를 선택하는 것은 설계 요구 조건을 충족하는 데 필수적입니다. 필요한 성능을 제공하는 것은 물론이고 업그레이드를 위한 여유도 있어야 합니다. 또한 널리 사용되는 기능을 위한 통합 주변장치를 활용하면 설계 과정을 단순화하고 부품 수를 줄일 수 있을 뿐 아니라 보드 공간도 절약할 수 있습니다.

마이크로칩은 주요 시스템 주변장치를 패키지에 통합해 CPU와 독립적으로 동작할 수 있도록 함으로써 MCU를 혁신했습니다. 이러한 코어 독립형 주변장치(core independent peripheral, CIP)는 CPU의 감독 없이 특정 작업을 처리할 수 있어, CPU가 슬립 모드에 들어가거나 다른 작업에 집중할 수 있게 해줍니다. 각 CIP는 안전 모니터링이나 파형 조정과 같은 특정 기능을 위해 설계되었으며, 애플리케이션에 맞게 사용자 정의가 가능합니다.

CIP는 CPU에 기반한 구현 방식보다 빠른 응답 시간, 줄어든 CPU 시간, 메모리 경합 감소 등의 장점을 제공합니다. 또한 설계 엔지니어가 전력이나 메모리 사용량을 최적화할 수 있도록 도와줍니다.

유연성 개선

일반적인 작업에 대해서는 CIP가 사전에 정의된 기능을 제공하긴 하지만, 일부 애플리케이션에서는 더 큰 유연성이 필요할 수 있습니다. 이때 구성 가능한 로직 블록(configurable logic block, CLB)이 활용됩니다. 특정 기능을 위해 설계된 CIP와 달리, CLB는 엔지니어가 필요에 따라 구성할 수 있는 완전히 사용자 정의 가능한 로직을 제공합니다.

마이크로칩은 CIP 접근법을 한 단계 더 발전시켜 PIC16F13145 MCU 제품군에 CLB를 도입했습니다. CIP와 마찬가지로, CLB 역시 코어와 독립적으로 동작하지만, 특정 기능이 정해져 있지는 않습니다. 재프로그래밍 가능한 로직 설계는 다양한 애플리케이션에 맞게 사용자 정의될 수 있습니다. CLB는 전력 소모 절감, 성능 향상, 고도로 통합된 설계 등 CIP의 모든 장점을 제공하면서, 엔지니어가 완벽한 맞춤형 애플리케이션을 구현할 수 있도록 지원합니다.

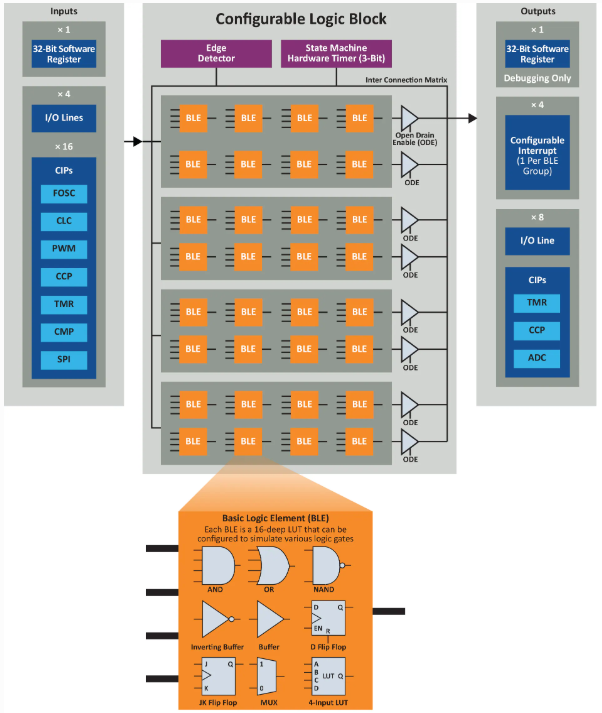

CLB 회로는 32개의 기본 로직 요소(basic logic element, BLE) 로 구성되어 있으며, 4개의 블록으로 배열되어 있습니다. 각 BLE는 AND/OR/NAND/NOR 게이트, 버퍼/인버팅 버퍼, D 플립플롭(flip-flop), J-K 플립플롭 또는 멀티플렉서를 시뮬레이션하도록 구성할 수 있습니다(그림 1).

-

그림 1. CLB(configurable logic block) 아키텍처는 BLE(basic logic element), I/O 연결성, 엣지 검출 및 상태 머신 타이머와 같은 하드웨어 기능을 갖추고 있어 임베디드 시스템의 유연성을 향상시킵니다. (출처: Microchip Technology)

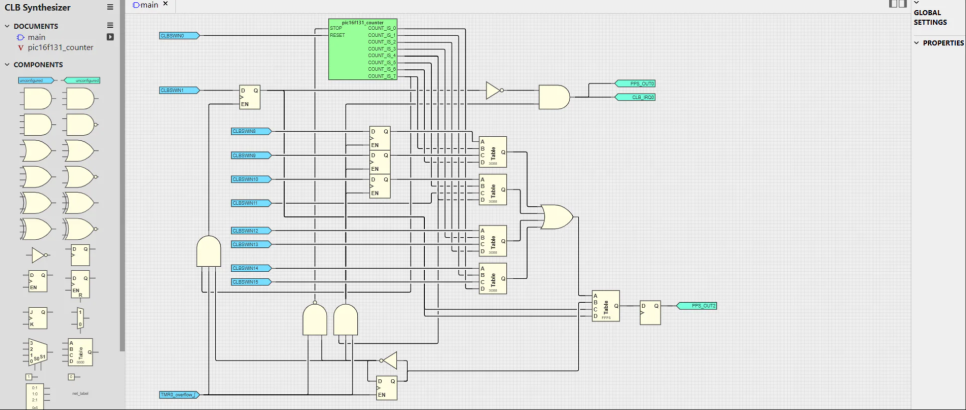

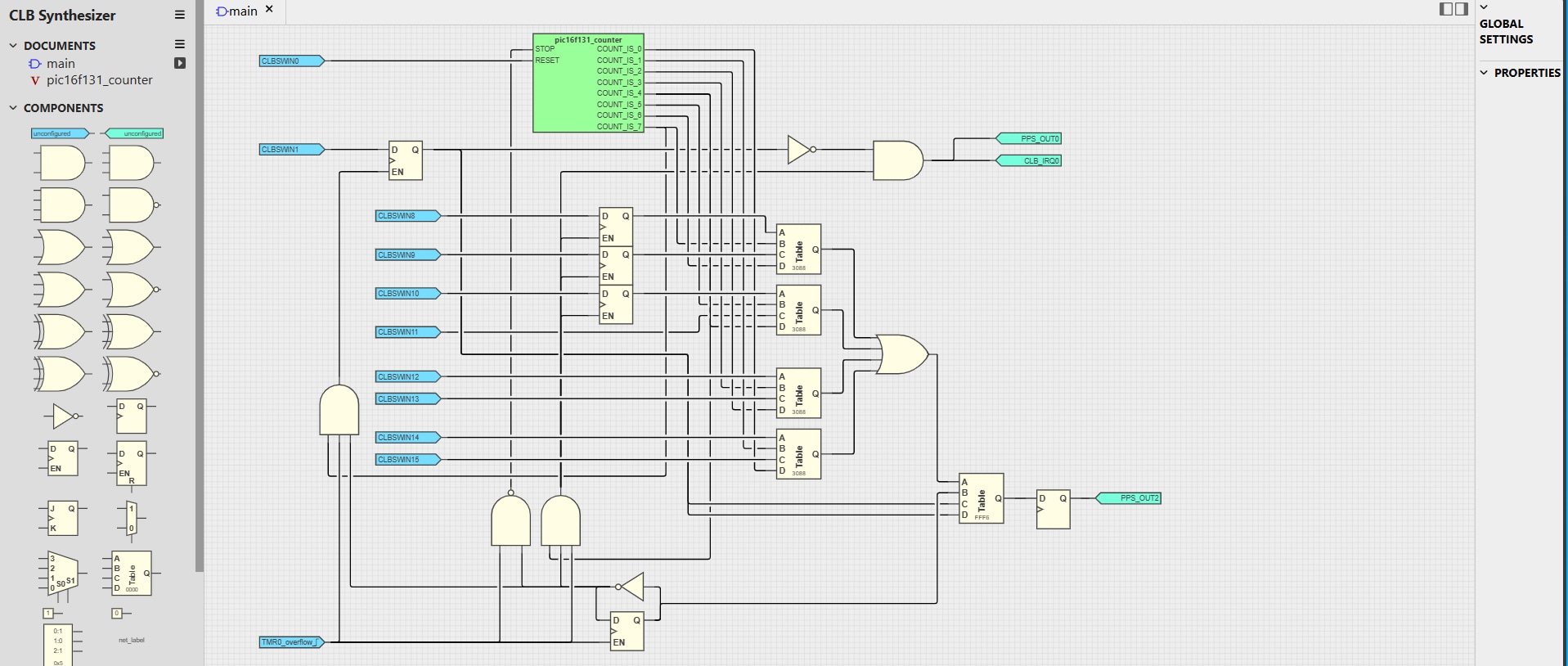

CLB는 또한 동적(on-the-fly) 구성 및 3상(tri-state) 로직을 지원합니다. 각 BLE는 내부적으로 다른 BLE 블록과 레지스터 및 카운터뿐만 아니라 외부 주변장치, I/O, 오실레이터 및 다른 CIP에 연결될 수 있습니다. 또한 각 BLE는 4입력 LUT(look-up table), 조합 로직, 플립플롭을 갖추고 있습니다. 마이크로칩의 MCC(MPLAB® Code Configurator)에 포함된 GUI 기반 CLB 그래픽 합성기를 사용하면 BLE 블록을 사용자가 설정할 수 있어, 복잡한 코딩 작업을 할 필요 없이 설계를 손쉽게 빌드하고 합성할 수 있습니다.

실제 CLB 예시

-

글루 로직(glue logic): 글루 로직은 CLB 기술의 장점을 보여주는 좋은 예시입니다. 오늘날 글루 기능 즉, 로직 게이트로 회로의 서로 다른 부분을 연결하거나 전압 레벨 시프팅을 수행하는 기능에는 디스크리트 부품이나 프로그래머블 로직이 사용됩니다. CLB 기술을 활용하면 이러한 작업을 추가적인 부품을 사용하지 않고도 빠르고 쉽게 수행할 수 있습니다. 또한 CLB의 프로그래머블 특성은 사용자가 필요에 따라 글루 로직을 재구성할 수 있도록 해줍니다.

-

인코딩 및 디코딩: CLB 기술이 장점을 발휘하는 또 다른 작업 예시로 인코딩과 디코딩 작업을 들 수 있습니다. 이들 작업은 반복적이므로 프로그래머블 로직에 적합합니다. 예를 들어, 전력과 데이터를 단일 와이어 쌍으로 동시에 전달할 수 있는 PoDL(power over data line) 통신이 점점 인기를 얻고 있습니다. PoDL은 맨체스터 코딩을 사용해, 송수신 간 데이터를 동기화하고 오류 검출을 수행함으로써 데이터 충실도를 보장합니다(그림 2). 디스크리트 인코더는 대형 수동소자들을 필요로 하기 때문에 솔루션의 크기와 비용을 증가시킵니다. 이에 반해 CLB 기술은 인코딩 과정을 가속화하고 더 빠른 데이터 전송 속도를 가능하게 해줍니다.

-

결함 감지(fault detection): CLB 기술은 결함 감지에 있어서 기존 기술에 비해 많은 이점을 제공합니다. 많은 회로들은 실시간으로 일반적인 결함을 확인하고, 결함이 발견되면 회로를 안전 상태로 전환해야 합니다. 이러한 검사는 회로의 동작 성능에 영향을 주지 않으면서 매우 빠르게 이루어져야 하므로, 빠른 응답과 예측 가능한 타이밍을 제공하는 하드웨어 기반 솔루션이 더 적합합니다. MCU에 기반한 소프트웨어로 오류를 감지하는 것은 어렵습니다. 왜냐하면 오류 상태가 언제 일어날지 타이밍을 미리 알 수 없고, 특수한 상황에서 드물게 발생하는 오류 때문에 소프트웨어 프로그램이 제대로 작동하지 않을 경우 안전 모드로 복귀하는 시간이 늦어질 수 있기 때문입니다. 이러한 경우를 대비하여 종종 디스크리트 프로그래머블 로직 디바이스를 사용하기도 하지만, 이는 그만큼 비용을 높일 뿐 아니라 디스크리트 통합을 위한 추가적인 설계 시간도 필요로 합니다. 이에 반해, CLB 기술은 단일 칩을 사용해 이와 동일하거나 또는 그보다 더 나은 성능을 제공할 수 있습니다.

-

타이밍 제어 및 전원 시퀀싱: 복잡한 임베디드 시스템에서는 타이밍 제어와 전원 시퀀싱 또한 매우 중요합니다. 전력 소비에 민감한 설계는 안정성을 보장하고 부품 손상을 방지하기 위해 정밀한 전원 인가 및 차단 순서가 필요합니다. 통상적으로 이 작업에는 외부 전원 시퀀싱 IC나 소프트웨어 제어 시퀀싱이 필요한데, 이는 과정이 복잡해지고 지연을 초래할 수 있습니다. 하지만 CLB를 사용하면 전원 시퀀싱 로직을 하드웨어에 직접 통합할 수 있어, 전원 레일이 올바른 순서로 활성화 및 비활성화되도록 보장하면서 지연을 최소화할 수 있습니다.

-

이중화(redundancy): CLB 기술은 시스템의 일부를 복제하여 하나의 장애 지점을 제거하는 데에도 활용될 수 있습니다. 예를 들어, MCU에서 수행되는 간단한 기능은 CLB 기반 백업을 가질 수 있으며, 이 로직 기반 백업은 만일 MCU 기능에서 소프트웨어 오류가 발생한다 하더라도 여전히 동작할 수 있습니다.

오늘날의 임베디드 시스템은 그 어느 때보다 더 복잡하고 전력 효율적으로 설계되고 있습니다. 그 결과, 뛰어난 처리 성능 그 이상의 기능을 제공하는 MCU가 필요해졌습니다. 이제 설계 엔지니어들은 우수한 프로세싱 성능과 유연성을 모두 요구합니다. 마이크로칩 테크놀로지의 CLB는 FPGA와 유사한 구성 가능성을 MCU에 제공하여 외부 부품을 줄이고, 성능을 향상시키며, 전력 효율을 최적화합니다.