최신 전력 변환 토폴로지를 적용한 SiC FET

역사적으로, 교류에서 직류로, 직류에서 교류로 전력을 변환하는 데 선호되는 방식이 있었습니다. 시간이 흐르면서 이들은 다양한 조건들로부터 제약을 받게 되었습니다. 예컨대, '역률 보정(power factor correction, PFC)'이 AC 배전에만 적용되어 AC/DC 전원 공급장치의 역률(PF)이 0.6 이하일 수 있었던 행복한 시절이 있었습니다. 그러다 1982년 무렵 유럽에는 법적 제한이 도입되었습니다. 그 결과, 정격 전력이 75W를 초과하는 전원공급장치 같은 일부 장비에는 '주전원 고조파 억제(mains harmonic suppression)'가 필요하지만, 조명 등 일부 애플리케이션에서는 이보다 더 낮은 조건이 요구됩니다.

-

(출처: UnitedSiC (현재 코보(Qorvo)에 합병)

이는 유니버설 입력 및 긴 라이드 스루 시간(long-ride-through time)과 같은 다른 기능을 가능하게 했지만, 실제로는 모든 AC/DC에 '부스트' 전력 변환 단계를 하나 더 추가하는 것이었기 때문에 제조사들에게는 부담일 수밖에 없었습니다. 최초의 회로들은 입력 인덕터, 스위치, 정류 다이오드를 포함하고 있었으며 변환 효율이 그다지 높지 않았습니다. 마찬가지로, 100W 이상의 AC/DC 내에서 DC/DC 변환 단계는 하프 브리지 또는 풀 브리지 형태의 간단한 포워드 컨버터로 시작했는데, 이는 비교적 이해하기가 쉽고 구현하는 것도 어렵지 않았지만 사용 가능한 반도체 기술과 토폴로지의 '하드 스위칭' 특성으로 인해 효율이 제한적이었습니다.

-

2004년 무렵부터 시행된 80 PLUS™ 인증 프로그램과 같은 성능 규격으로 인해 이러한 기본 PFC 및 DC/DC 변환 토폴로지는 시장에서 요구하는 효율 수준에 부적합해졌습니다. 예를 들어, 가장 높은 '티타늄' 레벨은 230VAC 장비에 대해 50% 부하에서 96%의 효율을 요구합니다. 이에 새로운 기법들이 발전해 왔으며, 현재 높은 전력 밀도와 효율을 위해 최대 수 kW까지 가능한 인기 있는 조합 방식은 공진형 'CLLC' 컨버터가 뒤에 붙는 '토템 폴 PFC(TPPFC)’ 스테이지입니다.

-

토템 폴 PFC(TPPFC) 스테이지

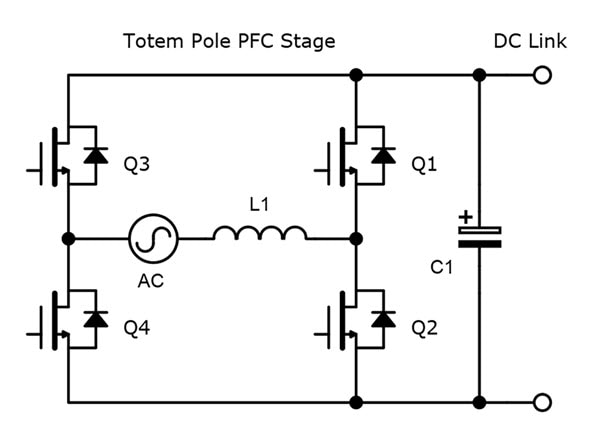

TPPFC는 반도체 스위치를 동기 정류기로 사용함으로써 AC/DC 프런트 엔드에서 입력 브리지 정류기를 효과적으로 제거합니다(그림 1). 중전력에서 대전력까지, 이 회로는 '연속 전도 모드(Continuous Conduction Mode, CCM)'로 작동하여 피크 전류를 관리가능한 상태로 유지하며, 그 결과 '하드 스위칭'이 발생합니다.

그림 1. '토템폴 PFC' 스테이지 회로 예시 (출처: UnitedSiC)

-

한쪽 주전원 극성에서는 Q1이 다이오드, Q2는 고주파 부스트 스위치로 작동하며, 다른 극성에서는 이 기능이 바뀝니다. Q3 및 Q4는 AC 라인 전류가 전원으로 돌아가는 경로를 제공하는 동기 다이오드 역할을 하며, 가격이 더 저렴한 디스크리트 다이오드를 사용할 수 있습니다. 전원 경로에는 스위치만 있으며, 여기서는 SiC FET로 표시되어 있으므로 전도 손실은 디바이스 온-저항에 의해서만 설정됩니다. Q1과 Q2에 Si-MOSFET을 사용할 경우, 데드타임(dead time) 동안 전도하는 바디 다이오드(body diode)의 역회복이 달성 가능한 효율을 제한할 수 있습니다. 하지만 이 위치에 UnitedSiC(현재 코보(Qorvo)에 합병됨)의 최신 750V Gen 4 18mΩ 부품과 같은 SiC FET를 사용하면 99.3%의 반도체 효율이 6.6kW 출력에서 달성되고, 75kHz에서 스위칭되며, Q1 및 Q2에서 각각 8.3W의 손실만 나타낼 수 있습니다. 이는 시장 선도적인 온-저항과 극도로 낮은 복구 손실 덕분입니다.

-

CLLC DC/DC 컨버터

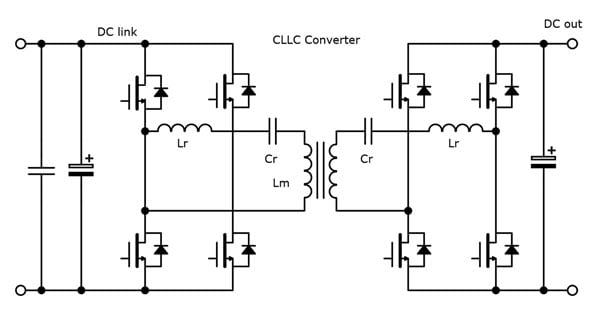

전체 효율 96%를 목표로 하는 TPPFC 스테이지는 훌륭한 출발점입니다. 메인 DC/DC 절연 스테이지의 경우, 널리 사용되는 'CLLC' 유형을 통해 공진 컨버터의 이점을 누릴 수 있습니다(그림 2).

그림 2. CLLC 컨버터 회로 예시 (출처: UnitedSiC)

-

CLLC는 각 스위치에 50% 듀티 사이클 드라이브가 있는 가변 주파수 컨버터이고 대칭형이므로 양방향 변환에 사용할 수 있습니다. 이 토폴로지는 공진형이므로, 1차측에서 제로 전압 스위칭을, 2차측에서 제로 전류 및 제로 전압 스위칭을 달성할 수 있습니다. 공진 컨버터에서는 스위칭 손실이 매우 낮고 바디 다이오드 복구가 문제가 되지 않으므로 주파수를 높여 마그네틱 크기를 최소화할 수 있습니다. 그렇다 하더라도 최소한의 '데드' 시간과 작동 범위를 결정하는 디바이스의 출력 커패시턴스 때문에, 이러한 영향력에는 한계가 있습니다. 다시 한 번 강조하지만, SiC FET는 고온 및 저온에서 특정 출력 커패시턴스 및 온-저항이 시중에서 가장 우수할 뿐만 아니라, 바디 다이오드 순방향 전압 강하가 매우 낮아 효율이 뛰어나다는 점에서 매우 이상적인 선택이 될 수 있습니다. 예를 들어 300kHz, 6.6kW에서 예제 PFC 스테이지에 사용된 것과 동일한 UnitedSiC 4세대 부품을 사용하면 99.8%의 반도체 효율을 얻을 수 있습니다. SiC FET의 또 다른 장점은 간편한 0 ~ 12V 게이트 드라이브입니다.

-

UnitedSiC는 설계자에게 성능 목표와 예산에 맞는 폭넓은 선택권을 제공하기 위해 다양한 패키지 옵션과 온-저항을 갖춘 다양한 750V 4세대 SiC FET 부품을 개발했습니다. 모든 옵션은 TI의 온라인 FET-Jet Calculator™를 통해 살펴볼 수 있으며, 이 계산기는 TPPFC 및 CLLC를 비롯한 다양한 선택 가능한 토폴로지의 SiC FET에 대한 즉각적인 성능 결과를 제공합니다. 여기에는 전력 소모, 온도 상승, 부품 스트레스 수준이 표시되며, 사용자는 여러 부품들을 병렬화하는 효과와 함께 전기 및 열 작동 조건을 지정할 수 있습니다.

이제 궁극의 토폴로지와 스위치를 갖추게 되었나요? 이제 우리는 스테이지 효율이 100%에 약간 부족한, 거의 100%에 근접한 상태입니다.